The world's first open switch ISA

XISAᵗᵐ (Xsight Instruction Set Architecture) is the programming specification for X-Switch silicon. Build custom network functions with full visibility into silicon behavior.

What is XISA

Just as x86 and Arm define how software interacts with CPUs, XISA defines how software interacts with Ethernet switch silicon. It's the first fully documented, openly available instruction set for programmable switching.

Like ARM for mobile

Standard ISA enables ecosystem

Like x86 for servers

Open architecture drives innovation

XISA for switches

First open switch standard

Business benefits of openness

Full transparency

No "black box" architectures. Understand exactly how your switch processes packets.

Build custom data planes

Create P4 data planes optimized for your specific use cases.

Extend without hardware

Add new protocol support in software without waiting for new silicon.

Community innovation

Benefit from ecosystem innovation and contribute back.

Avoid lock-in

Standard programming model across Xsight platforms.

Future-proof investment

Your code and expertise transfer across silicon generations.

Architecture overview

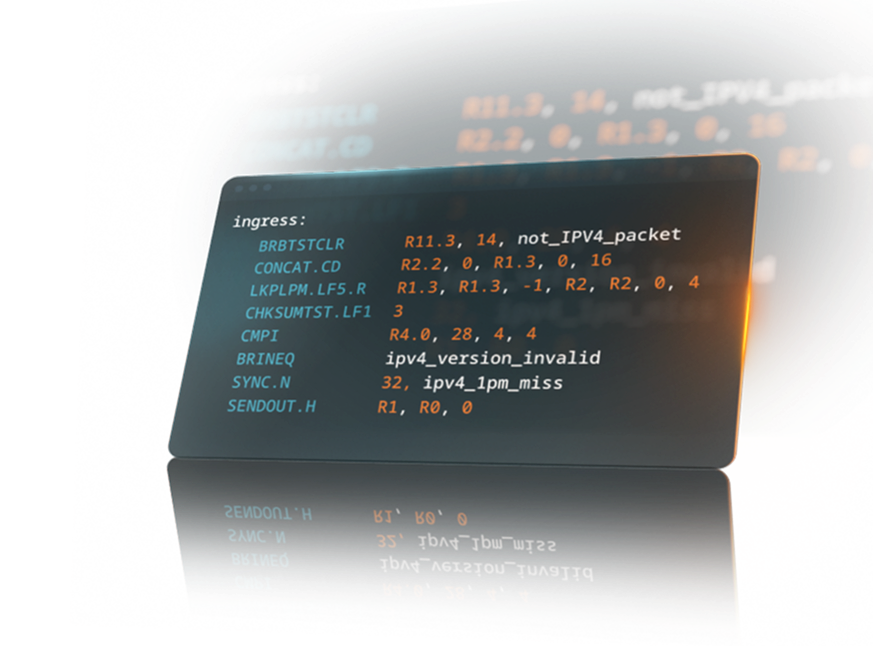

XISA consists of two instruction sets: Parser ISA for packet parsing and header extraction, and MAP ISA for the programmable match-action pipeline. Both execute in parallel across dedicated micro-engines.

Parser ISA

Walks header fields and generates lookup keys. Deterministic execution with protocol graph traversal.

MAP ISA

Handles packet processing with parallel threads and async accelerators. Flexible instruction ordering and elastic resource allocation.

Architecture comparison

Ready to get started?

Arrange a conversation with our solutions team to explore your infrastructure requirements and discover how open silicon can enhance your setup.